Main Content

Implement on Hardware

Prototype vision algorithms on Zynq® SoC devices

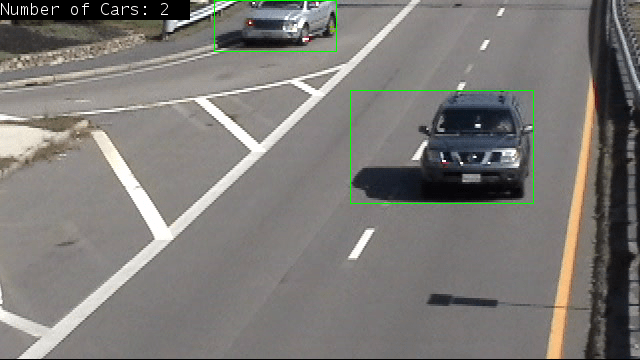

After you design and validate a pixel-streaming video processing algorithm in Simulink®, you can target the design to the FPGA on the Zynq board, and generate embedded ARM® code that interacts with the FPGA. You can route the video data to the ARM processor, and control AXI-Lite registers connected to the FPGA control logic.

Blocks

| Video Capture MIPI | Import live video frames from MIPI CSI-2 card on Zynq-based hardware (Since R2022b) |

| Video Capture HDMI | Import live video frames from HDMI FMC card on Zynq-based hardware (Since R2023a) |

| Draw Rectangle | Draw rectangles onto video frame stored in external memory (Since R2023a) |

| Set ROI | Draw over specified region of video frame stored in external memory (Since R2023a) |

Classes

visionzynq | Connect to Zynq hardware |

Functions

changeFPGAImage | Load image from on-board SD card into FPGA |

downloadImage | Write image to on-board SD card and load into FPGA |

Topics

FPGA and ARM Targeting

- Create Model Using Simulink Templates

Get started with a model configured for HDMI video processing. - Target FPGA on Zynq Hardware

FPGA targeting workflow using HDL Workflow Advisor. - Generate FPGA User Logic with AXI4-Stream Video Interface

Select an AXI4-Stream Video interface for your generated FPGA user logic. - Target an ARM Processor on Zynq Hardware

Design and deploy algorithms to the ARM processor. - Models Generated from FPGA Targeting

Run Simulink models that interact with the deployed algorithms running on the FPGA.

Memory Interface Modeling

- Model Frame Buffer Interface

Add external frame buffer to a pixel-streaming design. - Model AXI Manager Interface

Add random access memory interface to a pixel-streaming design. - Histogram Equalization with Zynq-Based Hardware

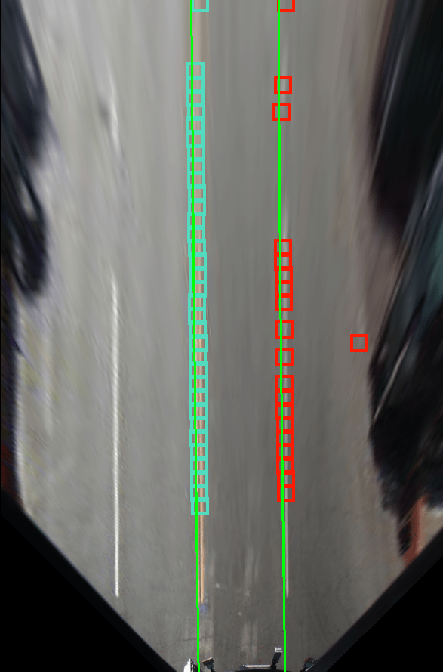

This example shows how to target histogram equalization algorithm to the Zynq® hardware using the SoC Blockset™ Support Package for AMD® FPGA and SoC Devices. - Pothole Detection with Zynq-Based Hardware

This example shows how to target a pothole detection algorithm to the Zynq® hardware using the SoC Blockset™ Support Package for AMD® FPGA and SoC Devices. - Image Rotation with Zynq-Based Hardware

This example shows how to target an image rotation algorithm to the Zynq® hardware by using the IP core generation workflow of the SoC Blockset™ Support Package for AMD® FPGA and SoC Devices.