Program functionality on FPGA, ASIC, or SoC hardware

Hardware design is the process by which functionality is programmed into custom circuitry. System and algorithm developers often begin hardware design in Simulink® and MATLAB® and then write a specification document that a hardware design team uses to manually create a hardware description language (HDL) implementation. The HDL representation is then used to program FPGA or ASIC hardware, which is often part of a System-on-a-Chip (SoC).

Manual writing of low-level HDL limits how broadly the hardware design team can explore different architectures, increases the number of bugs introduced, and limits the ability to reuse the algorithm for other projects.

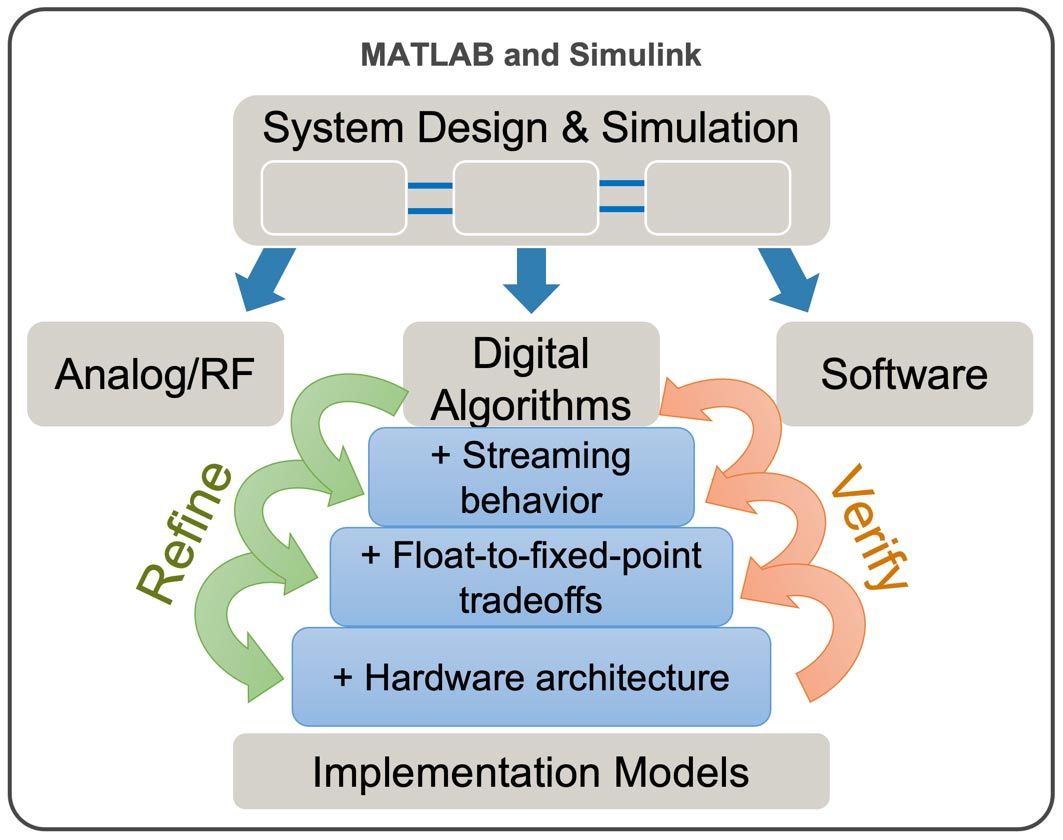

You can use MATLAB and Simulink to explore algorithms and determine which ones are most compute-intensive and could benefit from hardware design. You can then simulate the SoC architecture using SoC Blockset™.

You can also refine the hardware design through several steps, each of which can be verified against the previous step or the original algorithm:

- Adapt algorithms to process a continuous stream of data, which is how data typically flows through a hardware design

- Trade off numerical accuracy versus efficiency via fixed-point quantization or floating-point (9:19) implementation of hardware design components

- Add micro-architectures such as parallelism, timing, feedback loops, and other functionalities required to implement the hardware design

You can refine the hardware design using HDL-supported blocks and functions in Simulink and MATLAB. You can also use off-the-shelf DSP, wireless, video/image processing, or deep learning IP. Many developers use various combinations of all of these, depending on the application’s needs.

You can verify each step in the process versus the previous step or the original algorithm. You can re-use any of the representations to help the hardware design team verify their handwritten HDL code, via techniques such as cosimulation or verification component generation in HDL Verifier™. You can also prototype the hardware-ready implementation model on FPGA or SoC hardware connected to MATLAB or Simulink by running FPGA-in-the-loop testing.

In a fully connected hardware design workflow, you can use HDL Coder™ to generate functionally correct HDL code to begin the hardware design implementation process. This approach has the added advantage of full traceability back to the model and requirements, which is critical for functional safety workflows such as DO-254, ISO 26262, and IEC 61508.