AXI Manager

Note

MATLAB AXI master has been renamed to AXI manager. In the software and documentation, the terms "manager" and "subordinate" replace "master" and "slave," respectively.

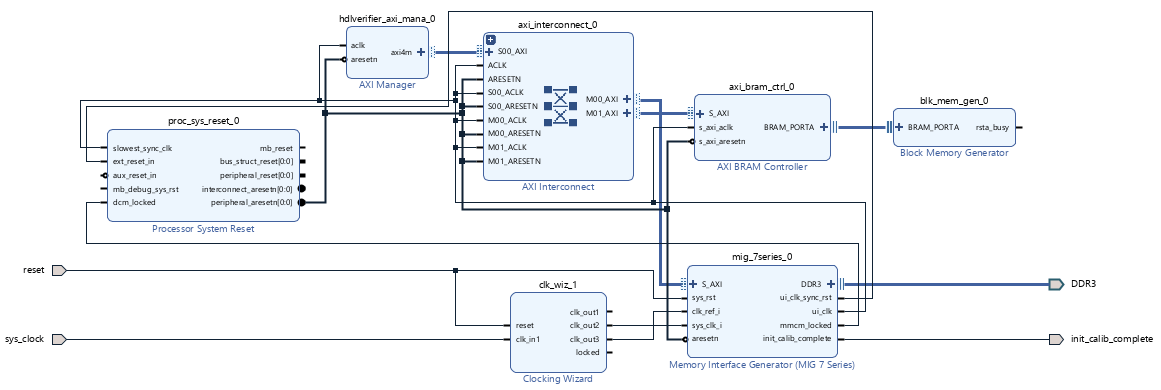

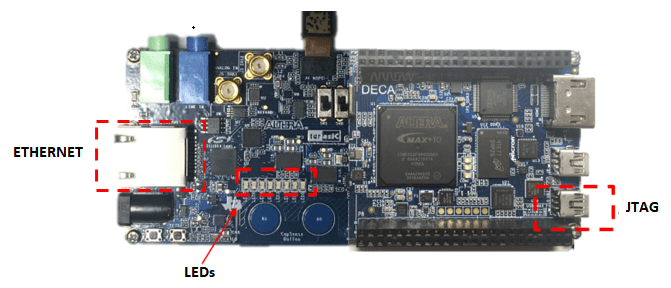

Access on-board memory locations from MATLAB or Simulink by using the AXI manager IP in your FPGA design. This IP connects to subordinate memory locations on the board. The IP also responds to read and write commands from MATLAB or Simulink, over JTAG, PCI Express®, or Ethernet cable. You can also access memory locations on Xilinx® boards from MATLAB over a USB Ethernet interface.

To use this feature, you must download a hardware support package for your FPGA board. See support package documentation. For an Intel® FPGA board, see AXI Manager. For a Xilinx FPGA board, see AXI Manager.

For information on downloading support packages, see Download FPGA Board Support Package.

Apps

| Logic Analyzer | Visualize, measure, and analyze transitions and states over time |

Topics

Overview

- Set Up AXI Manager

High-level steps for accessing memory-mapped locations on an FPGA board from MATLAB or Simulink.

AXI Manager Requirements and Preparation

- Download FPGA Board Support Package

The FPGA board support packages contain the definition files for all the supported boards for FPGA-in-the-loop (FIL) simulation, FPGA data capture, or AXI manager. - Set Up FPGA Design Software Tools

Set the MATLAB path to Xilinx, Microchip, and Intel software. - Guided Hardware Setup

Describes the steps in the automated support package setup process for configuring hardware for use with FPGA-in-the-loop, AXI manager, or FPGA data capture. - Configure Logic Analyzer

Adjust settings in the Logic Analyzer.