Generate an IP core from MATLAB and Simulink

A semiconductor intellectual property core – often referred to as an IP core – is a reusable HDL component for an FPGA, SoC FPGA, or ASIC design.

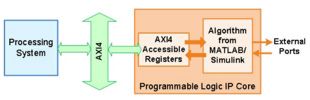

In FPGAs and SoC FPGAs, IP cores act as building blocks that you can integrate into complete implementations using design tools such as Vivado® IP Integrator and ISE from Xilinx or Qsys from Intel. The AMBA® AXI version 4 AXI interconnect protocol – better known as AXI4 – has emerged as a standard protocol for memory-mapped and streaming data transfer.

Common workflows for IP core generation produce IP cores that comply with the AXI4 interface supported by Xilinx and Intel and also the AXI4-Lite and AXI4-Stream protocols for Xilinx® devices. You can integrate these custom IP cores into FPGA or SoC FPGA designs with Xilinx Vivado IP Integrator or with Qsys from Intel.

You can do IP core generation from MATLAB® code or Simulink® models. You can also use the IP core generation workflow in HDL Coder™ with the C/C++ code generation features in Embedded Coder® in an automated hardware-software workflow that targets Xilinx Zynq® SoCs and Intel® SoC FPGAs.

For additional details, see HDL Coder™.

Examples and How To

Generating IP Cores for Intel FPGAs and SoC FPGAs

Generating IP Cores for Xilinx FPGAs and Zynq SoCs

Generating IP Cores for ASICs

Software Reference

Generating IP Cores for Intel SoC FPGAs

- Generate an IP Core for Intel SoC Platform from MATLAB - Documentation

- Generate an IP Core for Intel SoC Platform from Simulink - Documentation

Generating IP Cores for Xilinx Zynq SoCs

- Generate an IP Core for Zynq-7000 Platform from Simulink - Documentation

- Generate an IP Core for Zynq-7000 Platform from MATLAB - Documentation

- Model Design for AXI4-Stream Interface Generation - Documentation

See also: FPGA design and SoC codesign, Embedded Coder, HDL Coder, motor control design with Simulink, Xilinx Zynq support from Simulink, Intel SoC FPGA support from HDL Coder