Infraredx Accelerates FPGA Development on First-of-Its-Kind Intravascular Imaging System

Challenge

Solution

Results

- Development time reduced by months

- HDL code efficiency improved

- In-house FPGA implementation skills acquired

“bat365 Consulting Services helped us model our signal and image processing pipeline in Simulink, run simulations to verify that it was producing quality images, and then implement the design on an FPGA—all while ensuring that we acquired the know-how to do the work ourselves the next time.”

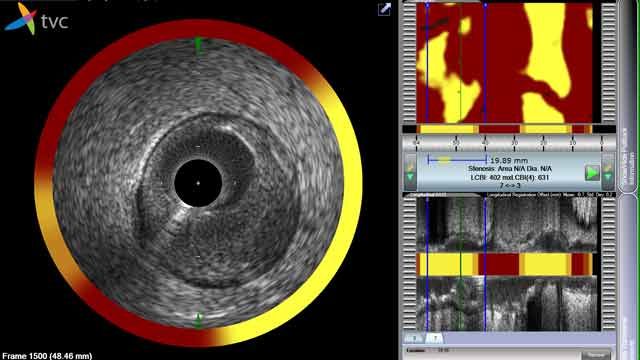

A patient with lipid core plaques (LCP) is more vulnerable to coronary artery disease (CAD), the number one killer in developed countries such as the United States. To help cardiologists detect LCP, Infraredx developed the TVC Imaging System™. The TVC Imaging System is the only FDA-approved medical device for LCP detection. It combines near-infrared spectroscopy (NIRS) with intravascular ultrasound (IVUS) in a single coronary catheter to provide information about vessel composition and structure.

Infraredx engaged bat365 Consulting Services to accelerate the development and FPGA implementation of the IVUS signal and image processing algorithms in the TVC Imaging System using MATLAB®, Simulink®, and HDL Coder™. “On the first project that we worked on with bat365 Consulting Services, we cut development time in half by generating HDL for our core IVUS algorithms,” says Dr. Zhihua He, principal imaging scientist at Infraredx. “More importantly the consultants taught us how we could accelerate FPGA implementation on future projects ourselves by using Simulink and HDL Coder.”

Challenge

Infraredx implemented the first version of its IVUS system by handwriting HDL code for an Intel® (formerly Altera®) Cyclone FPGA. Although the code was operational, hand-coding was not a feasible long-term solution. The Infraredx team relied on a contractor to implement enhancements and fixes to the HDL. This arrangement slowed development and made it impossible for Infraredx scientists to rapidly evaluate new ideas for their algorithms. Further, the initial implementation consumed almost all the multipliers and other resources on the FPGA, leaving virtually no room for the improved filters and other features that Infraredx had planned.

“We had the ability to develop image processing and signal processing algorithms, but we lacked the HDL proficiency to implement them on an FPGA,” says Dave Erickson, principal electrical engineer at Infraredx. “Outside companies were willing to help, but they wanted to do the work for us from start to finish. Our goal was to develop the expertise in-house so that we could do the work ourselves.”

Solution

Infraredx worked with bat365 Consulting Services to speed the development and FPGA implementation of the next-generation IVUS system. bat365 consultants provided training to enable Infraredx engineers and scientists to use Simulink and HDL Coder themselves on future versions of the product.

Infraredx scientists and engineers developed their initial algorithms in MATLAB. The team of Infraredx scientists and bat365 Consulting Services created a Simulink model based on these algorithms, using Simulink blocks to implement FIR filters, IIR filters, and other elements of the signal and image processing pipeline. They ran simulations and verified the Simulink model by comparing its output with the output produced by the MATLAB algorithms.

Using Fixed-Point Designer™, they converted the floating-point Simulink model to fixed point, and performed bit-true simulations to evaluate the effects of precision adjustments on image quality.

The team demonstrated the validated model to Infraredx management. At this milestone, management committed to using HDL Coder for the FPGA implementation.

To implement the design on the Cyclone FPGA, the team generated VHDL® code from the Simulink model with HDL Coder. They then optimized the model, adding multiple synchronous clocks to make the most efficient use of available FPGA resources.

The group verified the FPGA implementation by comparing its output with the MATLAB simulation results.

Working independently, Infraredx scientists and engineers then completed a third version of the IVUS system, which included higher image resolution, increased depth penetration, and enhanced tissue features. The group is currently using Simulink and HDL Coder for continued improvement of the TVC Imaging System.

Results

Development time reduced by months. “The first version of our IVUS processing pipeline took six months to develop,” says Dr. He. “With Simulink and HDL Coder, the second generation was completed in three months and the third in six weeks.”

HDL code efficiency improved. The generated HDL used the same number of multipliers as the handwritten HDL while using 9% less logic and 3% less memory. “HDL Coder enabled us to add a significant amount of functionality—including twice as many filters—and still fit our design on the same FPGA,” says John Beck, principal software engineer at Infraredx.

In-house FPGA implementation skills acquired. “With help from bat365 Consulting Services, our algorithm developers and image processing specialists now know how to implement their ideas on an FPGA,” says Erickson. “It’s a tremendous advantage to simulate a design change in Simulink, generate the HDL, and test it in real time on the FPGA within 30 minutes.”